- 您现在的位置:买卖IC网 > Sheet目录509 > SI4313-B1-FM (Silicon Laboratories Inc)IC RX FSK 315-915MHZ 20VQFN

�� �

�

Si4313-B1�

�3.2.3.� RX� State�

�The� RX� state� may� be� entered� from� any� of� the� Idle� modes� when� the� rxon� bit� is� set� to� 1� in� 'Register� 07h.� Operating�

�Mode� and� Function� Control� 1'.� A� built-in� sequencer� takes� care� of� all� the� actions� required� to� transition� from� one� of�

�the� IDLE� modes� to� the� RX� state.� The� following� sequence� of� events� will� occur� automatically� to� get� the� chip� into� RX�

�mode� when� going� from� STANDBY� mode� to� RX� mode� by� setting� the� rxon� bit:�

�1.� Enable� the� main� digital� LDO� and� the� Analog� LDOs.�

�2.� Start� up� crystal� oscillator� and� wait� until� ready� (controlled� by� internal� timer).�

�3.� Enable� PLL.�

�4.� Calibrate� VCO� (this� action� is� skipped� when� the� vcocal� bit� is� "0",� default� value� is� "1").�

�5.� Wait� until� PLL� settles� to� required� receive� frequency� (controlled� by� internal� timer).�

�6.� Enable� receive� circuits:� LNA,� mixers,� and� ADC.�

�7.� Calibrate� ADC� (RC� calibration).�

�8.� Enable� receive� mode� in� the� digital� modem.�

�Depending� on� the� configuration� of� the� radio� all� or� some� of� the� following� functions� will� be� performed� automatically� by�

�the� digital� modem:� AGC,� AFC� (optional),� update� status� registers,� bit� synchronization,� packet� handling� (optional)�

�including� sync� word,� header� check,� and� CRC.�

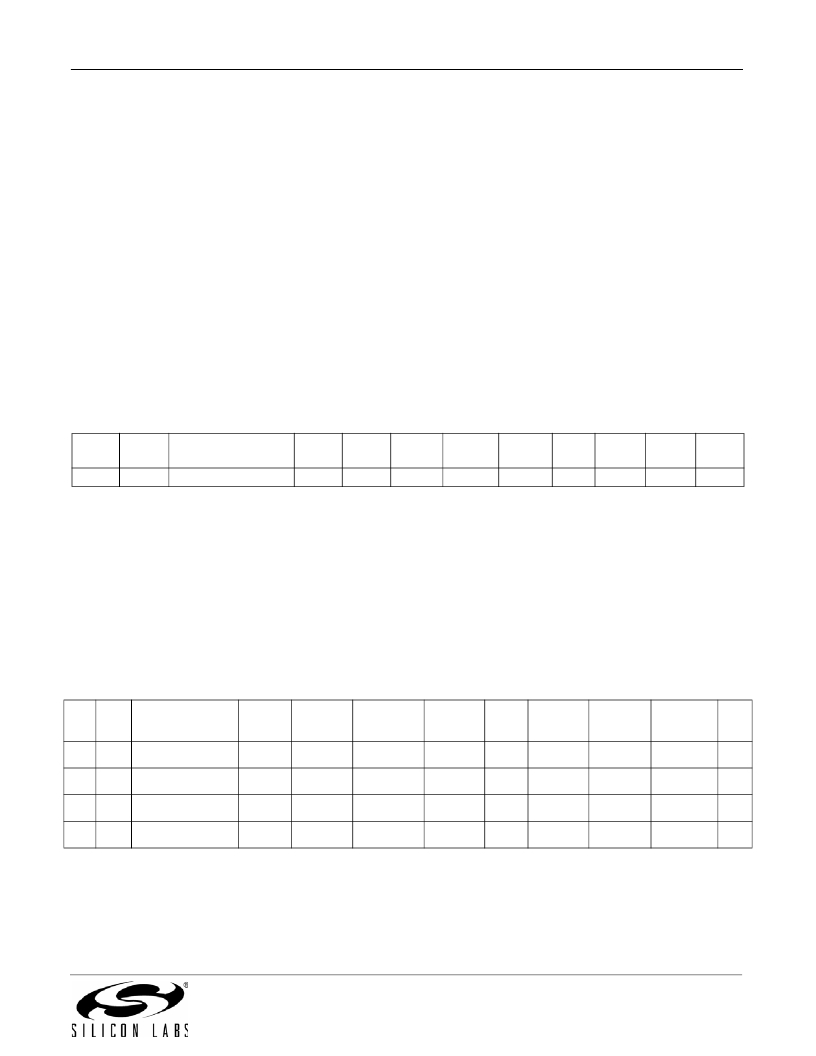

�3.2.4.� Device� Status�

�Add�

�R/W�

�Func/Description�

�D7�

�D6�

�D5�

�D4�

�D3�

�D2�

�D1�

�D0�

�POR�

�Def�

�02�

�R�

�Device� Status�

�ffovfl�

�ffunfl�

�rxffem� Reserved� freqerr�

�cps[1]�

�cps[2]�

�—�

�The� operational� status� of� the� Si4313� can� be� read� from� the� Device� Status� register,� 'Register� 02h'�

�3.3.� Interrupts�

�The� Si4313� is� capable� of� generating� an� interrupt� signal� when� certain� events� occur.� The� chip� notifies� the�

�microcontroller� that� an� interrupt� event� has� occurred� by� setting� the� nIRQ� output� pin� LOW� =� 0.� This� interrupt� signal�

�will� be� generated� when� any� one� (or� more)� of� the� interrupt� events� (corresponding� to� the� Interrupt� Status� bits)� shown�

�below� occur.� The� nIRQ� pin� will� remain� low� until� the� microcontroller� reads� the� Interrupt� Status� Register(s)� (Registers�

�03h-04h)� containing� the� active� Interrupt� Status� bit.� The� nIRQ� output� signal� will� then� be� reset� until� the� next� change� in�

�status� is� detected.� The� interrupts� must� be� enabled� by� the� corresponding� enable� bit� in� the� Interrupt� Enable�

�Registers� (Registers� 05h-06h).� All� enabled� interrupt� bits� will� be� cleared� when� the� microcontroller� reads� the� interrupt�

�status� register.� If� the� interrupt� is� not� enabled� when� the� event� then� it� will� not� trigger� the� nIRQ� pin,� but� the� status� may�

�still� be� read� at� anytime� in� the� Interrupt� Status� registers.�

�Add� R/W� Func/Description�

�D7�

�D6�

�D5�

�D4�

�D3�

�D2�

�D1�

�D0�

�POR�

�Def�

�03�

�R�

�Interrupt� Status� 1�

�ifferr�

�Reserved�

�Reserved�

�irxffafull�

�iext�

�Reserved� Reserved�

�Reserved�

�—�

�04�

�R�

�Interrupt� Status� 2�

�iswdet�

�ipreaval�

�ipreainval�

�irssi�

�iwut�

�ilbd�

�ichiprdy�

�ipor�

�—�

�05�

�R/W� Interrupt� Enable� 1�

�enfferr�

�Reserved�

�Reserved�

�enrxffafull� enext� Reserved� Reserved�

�Reserved�

�00h�

�06�

�R/W� Interrupt� Enable� 1� enswdet� enpreaval� enpreainval�

�enrssi�

�enwut�

�enlbd�

�enchiprdy�

�enpor�

�01h�

�Rev.� 1.0�

�21�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SI4320-J1-FT

IC RCVR FSK 915MHZ 5.4V 16-TSSOP

SI4322-A0-FT

IC RX FSK UNI 868/915MHZ 16TSSOP

SI4324DY-T1-GE3

MOSFET N-CH D-S 30V 8-SOIC

SI4330-B1-FM

IC RCVR ISM 960MHZ 3.6V 20-QFN

SI4354DY-T1-GE3

MOSFET N-CH D-S 30V 8-SOIC

SI4355-B1A-FM

IC EZRADIO FM RECEIVER SI4355

SI4388DY-T1-GE3

MOSFET DUAL N-CH 30V 8-SOIC

SI4390DY-T1-GE3

MOSFET N-CH 30V 8.5A 8SOIC

相关代理商/技术参数

SI4313-B1-FMR

功能描述:射频接收器 240-960 MHz Receiver RoHS:否 制造商:Skyworks Solutions, Inc. 类型:GPS Receiver 封装 / 箱体:QFN-24 工作频率:4.092 MHz 工作电源电压:3.3 V 封装:Reel

SI4315-A0-FT

功能描述:射频接收器 Receivers - IA4315 RoHS:否 制造商:Skyworks Solutions, Inc. 类型:GPS Receiver 封装 / 箱体:QFN-24 工作频率:4.092 MHz 工作电源电压:3.3 V 封装:Reel

SI4320DY

制造商:VISHAY 制造商全称:Vishay Siliconix 功能描述:N-Channel 30-V (D-S) MOSFET

SI4320DY-T1

功能描述:MOSFET 30V 25A 1.6W RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube

SI4320DY-T1-E3

功能描述:MOSFET 30V 25A 3.5W 3.0mohm @ 10V RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube

SI4320DY-T1-GE3

功能描述:MOSFET 30V 25A 3.5W 3.0mohm @ 10V RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube

SI4320-J1-FT

功能描述:射频接收器 Receivers - IA4320 RoHS:否 制造商:Skyworks Solutions, Inc. 类型:GPS Receiver 封装 / 箱体:QFN-24 工作频率:4.092 MHz 工作电源电压:3.3 V 封装:Reel

SI4320-J1-FTR

功能描述:射频接收器 Receiver (EZRadio) RoHS:否 制造商:Skyworks Solutions, Inc. 类型:GPS Receiver 封装 / 箱体:QFN-24 工作频率:4.092 MHz 工作电源电压:3.3 V 封装:Reel